Arasan announces the immediate availability of its 2’nd generation of CAN IP for the CAN 2.0 and CAN FD Specifications. The controllers have been rearchitected and upgraded to lower power consumption and area, which make them suitable for FPGA applications in addition to Arasan’s primary ASIC IP market. Although automobiles do not have stringent power requirements like […]

FPGA

IP core modules facilitate reuse of SoC, MCU, FPGA and ASIC functions

The Fraunhofer Institute for Photonic Microsystems IPMS offers ready-made, platform-independent IP core modules. With IP modules, developers can quickly adopt complete functional areas in standard products such as SoCs, microcontrollers, FPGAs and ASICs. This allows a significant reduction of development times and costs. With EMSA5, Fraunhofer IPMS offers a processor core based on the open […]

Rad-hard eFPGA IP works with 90-nm rad-hard fab process

QuickLogic Corporation announced it has teamed with SkyWater Technology to make a “fast boot” rad-hard eFPGA IP available to users of SkyWater’s 90 nm rad-hard (RH90) process. This technology can be embedded as an IP core in ASIC and SoC devices or implemented as a custom rad-hard FPGA for mission-critical and/or ruggedized applications. QuickLogic’s eFPGA […]

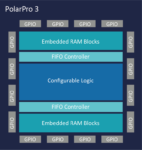

SRAM-based FPGAs feature 55-uA consumption, tiny footprint

QuickLogic Corporation announced that its PolarPro 3 family of low power, SRAM-based FPGAs are available to solve semiconductor supply availability challenges. This highly flexible family features power consumption as low as 55uA and a tiny footprint in small packages, as well as die options. Packed into the small physical die size is up to 2,000 effective logic cells […]

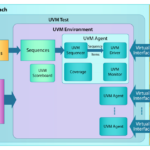

Automatic UVM generator function added to high-performance ASIC/large FPGA verification software

Aldec, Inc. has added an automatic UVM Generator function to Riviera-PRO. The addition promises to greatly boost the productivity of Riviera-PRO users taking advantage of the benefits of the Universal Verification Methodology, which contains guidance on the creation and reuse of verification test benches. Riviera-PRO’s new function automatically creates the UVM testbench (in SystemVerilog, the […]

Low-power FPGAs target cost-sensitive applications

The ForgeFPGA Family will address the underserved market need for relatively small amounts of programmable logic that can be quickly and efficiently designed into cost-sensitive applications. The ForgeFPGA devices will provide dramatic cost savings versus other alternatives, including non-FPGA designs. By providing a high level of integration, they reduce overall board and system costs. Their […]

IP generator enables rapid prototyping of customizable FPGA architectures

QuickLogic Corporation announced its new Australis embedded FPGA (eFPGA) IP Generator. This groundbreaking tool is a culmination of the company’s three decades of deep domain expertise in designing and shipping programmable logic architectures that are silicon-efficient, reliable, high quality, and manufacturable at scale, implemented using the silicon automation design techniques of the OpenFPGA open-source framework. […]

PCIe 5.0 digital controller supports up to 32 GT/sec data rates

Rambus Inc. announced that Rambus has demonstrated its PCI Express (PCIe) 5.0 digital controller IP on leading FPGA platforms. PCIe 5.0 performance at 32 GT/s in FPGAs using a soft controller is an industry first, and another demonstration of technical leadership from Rambus. This capability expands the use models of FPGAs by enabling multi-instance, switching, and bridging […]

FPGAs optimized for infotainment, ADAS, safety system use

Lattice Semiconductor expanded its growing portfolio of automotive products with the announcement of versions of the Lattice Certus-NX FPGA family optimized for infotainment, advanced driver assistance systems (ADAS), and safety-focused applications. Built on the Lattice Nexus platform, these new Certus-NX devices combine automotive-grade features with best-in-class I/O density, power efficiency, small size, reliability, instant-on performance, and support for fast PCI Express (PCIe) […]

Dev kit handles unallocated Xilinx FPGA resources

The Hardware Development Kit (HDK) is a tool allowing users to develop unallocated Xilinx, Inc. FPGA resources on Abaco boards. The HDK uses specific features in the new Xilinx Vivado ML Editions tool suite which allow users to implement custom intellectual property (IP) while maintaining the overall integrity of the Abaco IP. Building on the […]