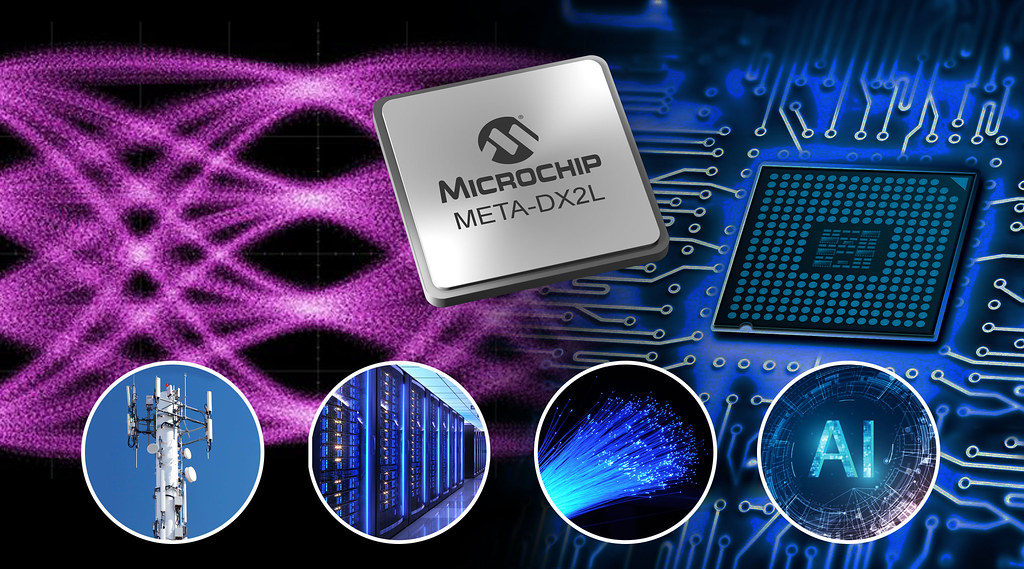

Routers, switches, and line cards need higher bandwidth, port density, and up to 800 Gigabit Ethernet (GbE) connectivity to handle escalating data center traffic driven by 5G, cloud services, and Artificial Intelligence (AI) and Machine Learning (ML) applications. To deliver the higher bandwidth, these designs need to overcome the signal integrity challenges associated with the industry’s transition to the 112G (gigabits per second) PAM4 Serializer/Deserializer (SerDes) connectivity that is needed to support the latest pluggable optics, system backplanes, and packet processors. These challenges can now be overcome with the industry’s most compact, 1.6T (terabits per second), low-power PHY (physical layer) solution from Microchip Technology Inc. with its PM6200 META-DX2L that reduces power per port by 35 percent compared to its 56G PAM4 predecessor, META-DX1, the industry’s first terabit-scale PHY solution.

Routers, switches, and line cards need higher bandwidth, port density, and up to 800 Gigabit Ethernet (GbE) connectivity to handle escalating data center traffic driven by 5G, cloud services, and Artificial Intelligence (AI) and Machine Learning (ML) applications. To deliver the higher bandwidth, these designs need to overcome the signal integrity challenges associated with the industry’s transition to the 112G (gigabits per second) PAM4 Serializer/Deserializer (SerDes) connectivity that is needed to support the latest pluggable optics, system backplanes, and packet processors. These challenges can now be overcome with the industry’s most compact, 1.6T (terabits per second), low-power PHY (physical layer) solution from Microchip Technology Inc. with its PM6200 META-DX2L that reduces power per port by 35 percent compared to its 56G PAM4 predecessor, META-DX1, the industry’s first terabit-scale PHY solution. With its high-density 1.6T bandwidth, space-saving footprint, 112G PAM4 SerDes technology, and support for Ethernet rates from 1 to 800 GbE, Microchip’s META-DX2L Ethernet PHY is an industrial-temperature-grade device that offers the connectivity versatility to maximize design reuse across applications ranging from a retimer, gearbox or reverse gearbox to a hitless 2:1 multiplexor (mux). Highly configurable crosspoint and gearbox features make full use of a switch device’s I/O bandwidth to enable the flexible connections necessary for multi-rate cards that support a wide range of pluggable optics. The PHY’s low-power PAM4 SerDes enables it to support the next-generation infrastructure interface rate for cloud data centers, AI/ML compute clusters, 5G, and telecom service provider infrastructure, whether over long-reach direct attach copper (DAC) cables, backplanes, or connections to pluggable optics.

META-DX2L is offered in the industry’s smallest package size, 23 x 30 millimeter (mm), which enables the space savings necessary to deliver the line card port densities demanded by hyperscalers and system developers. Product highlights include Dual 800 GbE, Quad 400 GbE, and 16x 100/50/25/10/1 GbE PHY; Supports Ethernet, OTN, and Fibre Channel data rates; Supports proprietary data rates for AI/ML applications; Integrated 2:1 hitless mux enables high availability/protection architectures; Highly configurable crosspoint supporting multi-rate services on any port; Constant latency, enabling IEEE 1588 Class C/D PTP at the system level; FEC termination, monitoring, and conversion between various interface rates; 32 long-reach (LR) capable 112G PAM4 SerDes with programmability to optimize power vs. performance; Support for DAC cables, including auto-negotiation and link training; Industrial-temperature-range support, enabling deployments in outdoor environments; Complete Software Development Kit (SDK) with a hitless upgrade and warm restart capabilities and compatible with the field-proven META-DX1 SDKl;

Microchip provides a full set of design-in collateral, reference designs, and evaluation boards to support customers’ building systems with META-DX2L devices. In addition to Ethernet PHY technology, Microchip also provides system vendors with a total system solution including PolarFire FPGAs, the ZL30632 high-performance PLL, oscillators, voltage regulators, and other components that have been pre-validated as a system with META-DX2L to help bring designs to production faster.

Initial META-DX2L devices are expected to sample during the fourth calendar quarter of 2021.