Agile Analog has launched its first range of analog subsystems, covering power management, PVT sensing, and sleep management. These innovative, digitally wrapped subsystems significantly reduce the effort required to integrate multiple analog IPs into any ASIC by allowing the IP to be dropped straight into a digital design flow and connected via a standard peripheral […]

agileanalog

Analog macro cores wrap around MPU, memory chip IP

Agile Analog now has available a complete set of the key analog IP needed to fast-track an IoT design. Arranged in six blocks, they wrap around the customer’s choice of processor core and memory to provide all the vital analog functions required to interface between the digital world of the processor and the analog real […]

Digital standard cell library available in thick-oxide-based cells

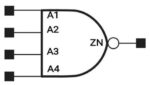

Agile Analog has launched its Digital Standard Cell Library (DSCL). It provides a comprehensive library of digital cells enabling designers to implement the digital circuits required to control analog blocks in mixed-signal solutions. The new digital library is available in thick-oxide-based cells, operating above the core voltage domain, minimizing leakage and allowing easy migration across […]

IP detects power fluctuations in chip designs

Agile Analog has designed an IR Drop Sensor for its growing library of analog IP. This is an important safety feature for designers as it monitors for voltage drops when current flows through a resistor, which is called IR drop, and can affect the timing of a chip and could result in functional failures if […]