Synopsys, Inc. introduced its complete DesignWare High Bandwidth Memory 2 (HBM2) IP solution consisting of controller, PHY and verification IP, enabling designers to achieve up to 307 GB/s aggregate bandwidth, which is 12 times the bandwidth of a DDR4 interface operating at 3200 Mb/s data rate. In addition, the DesignWare HBM2 IP solution delivers approximately ten times better […]

synopsys

Chip design IP emphasizes software integrity and security

Synopsys, Inc. announced key updates to its Software Integrity Platform that are designed to help companies build security and quality into their software while reducing time-to-market. In the era of digital transformation, building secure and reliable software is challenged by the rapid, complex and diverse nature of development cycles. The latest updates to the Synopsys Software Integrity Platform […]

Chip design IP now works with 7-nm Leading-Performance (7LP) FinFET process

Synopsys, Inc. today announced the enablement of the Synopsys Design Platform and DesignWare® Embedded Memory IP on GLOBALFOUNDRIES 7-nm Leading-Performance (7LP) FinFET process technology. Synopsys and GF collaboration on the new process addressed several new challenges specific to the 7LP process. This process is expected to deliver 40 percent more processing power and twice the area scaling […]

Verification IP, source-code test suite works with ARM AMBA 5 Coherent Hub Interface Issue B

Synopsys, Inc. today announced the availability of its Verification IP (VIP) and source code test suite for ARM® AMBA® 5 Coherent Hub Interface (CHI) Issue B. Synopsys VC VIP for AMBA CHI has been widely adopted by SoC leaders for successful verification closure and tape out of coherent subsystems and interconnects. Synopsys VIP for the latest AMBA CHI Issue B specification enables […]

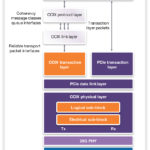

Controller, PHY and verification IP hits 25Gbps, supports cache-coherency for high-performance cloud computing

Synopsys, Inc. announced immediate availability of its complete DesignWare CCIX IP solution, consisting of controller, PHY and verification IP delivering data transfer speeds up to 25Gbps and supporting cache-coherency for high-performance cloud computing applications. The Cache Coherent Interconnect for Accelerators (CCIX) standard allows accelerators and processors to access shared memory in a heterogeneous multi-processor system for […]

Multi-Protocol 25G PHY IP handles high-performance computing applications

Synopsys, Inc. announced its new DesignWare® Multi-Protocol 25G PHY IP for high-performance computing applications including machine learning and artificial intelligence. The PHY IP gives designers the flexibility to efficiently integrate multiple protocols including PCI Express® 4.0, 25G Ethernet, SATA and CCIX into system-on-chips (SoCs) targeting the 7-nanometer (nm) and 16-nm FinFET processes. The multi-protocol 25G PHY reduces power and […]

The post Multi-Protocol 25G PHY IP handles high-performance computing applications appeared first on Microcontroller Tips.

High-performance RISC processors add 2x DSP performance

Synopsys, Inc. announced the availability of the new DesignWare ARC HS4x and HS4xD processor family for high-performance embedded applications. The ARC HS44, HS46, HS48, HS45D and HS47D processors, available in single-, dual- and quad-core configurations, implement a dual-issue superscalar architecture that delivers up to 6000 DMIPS per core, making it the highest performance processor in the popular ARC HS […]

The post High-performance RISC processors add 2x DSP performance appeared first on Microcontroller Tips.

Simulator handles early gate-level power analysis to within 5% of power signoff

Synopsys, Inc. announced the availability of its PowerReplay solution to enable early and fast gate-level power analysis with accuracy within 5% of power signoff. Energy efficiency has become a key criterion in complex designs that increasingly need to achieve stricter power targets. The new PowerReplay solution, in combination with Synopsys PrimeTime PX gate-level power analysis, […]

Circuit simulators make faster work of AMS designs

Synopsys, Inc.today announced the release of the latest versions of its HSPICE, FineSim and CustomSim circuit simulation products. The growth in automotive electronics and transition to FinFET process nodes have led to a significant increase in IC design complexity and the need for rigorous analysis to validate design robustness across a broad set of design […]

The post Circuit simulators make faster work of AMS designs appeared first on Analog IC Tips.

VIP and source code test suite handles MIPI designs

Synopsys, Inc. announced the availability of the industry’s first verification IP (VIP) and source code test suite for MIPI CSI-2℠ v2.0, MIPI D-PHY℠ v2.1, MIPI C-PHY℠ v1.2, and MIPI M-PHY℠ v4.1. Synopsys VC VIP for the latest MIPI specifications enables system-on-chip (SoC) teams to design next-generation mobility products with ease of use and integration, resulting in accelerated verification closure. “MIPI […]

The post VIP and source code test suite handles MIPI designs appeared first on Microcontroller Tips.