Chiplets enable heterogeneous integration of various process nodes and materials to maximize performance. UCIe is a new die-to-die interconnect standard for high-bandwidth, low-latency, power-efficient, and cost-effective connectivity between chiplets. UCIe is also the first specification to include an interface that is compatible with optical links.

Large computing systems needed to support high-performance computing (HPC) applications like artificial intelligence (AI) and machine learning (ML) are becoming increasingly difficult to build. In conventional architectures, the density of compute and memory resources is increasing, creating bandwidth bottlenecks and interconnect challenges. High hardware density also causes power and cooling challenges.

Disaggregation and optical interconnects

Optical interconnects can support much higher bandwidths compared with copper. That can enable compute and memory resources to be disaggregated and spread out, supporting flexible, dynamic resource allocation and improved power and thermal performance.

But that’s only a short-term solution. The bandwidth bottleneck is expected to migrate from the data center and rack levels into individual chiplets. Today, optical interconnects are needed to support chiplet connectivity with the wider system. Next, copper interconnects will be insufficient inside chiplets and will need to be replaced with optical solutions.

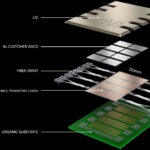

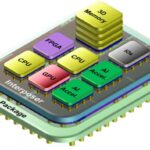

Chiplets provide designers with a new tool for dealing with the need for higher performance by supporting a sea of heterogeneous cores and 3D stacked memory (Figure 1). That’s great, but it also drives up demands for high bandwidth, low latency, power efficiency, and cost-effective interconnects.

Compute express link

UCIe is complementary to the higher-layer compute express link (CXL) protocol. CXL was designed to run on a PCIe physical layer and support rack and data center connectivity. It has been expanded to work with the UCIe physical layer. That’s intended to support off-chip connectivity from the rack level and higher using UCIe retimmers to support optical interconnects. The combination of CXL and UCIe optical interconnects is expected to support lower power, lower latency, and higher bandwidths than can be achieved using active optical cabling and Ethernet.

The UCIe and CXL groups are working to expand optical-related I/O specifications. For example, UCIe supports resource pooling or aggregation in data centers within blade servers using PCIe/CXL I/O chips or rack-to-rack using optical chips that integrate UCIe.

In one case, an optical I/O chiplet, using a custom interface bus, has been developed that’s UCIe compatible and designed to support the next generation of HPC compute architectures on chiplets. This solution includes an in-package optical I/O (OIO) chiplet and a laser light source that can fit into a UCIe-compatible platform. Each OIO chiplet supports a bandwidth of up to 2 Terabits/second (Tbps), the equivalent of 64 PCIe Gen5 lanes.

In another example of optical interconnects for chiplets, arrays of micro-LEDs have been 3D stacked onto a CMOS interface IC that bundles silicon detectors. This new optical interconnect architecture enables low-power links with under 1pJ/bit and up to 10m reach. The parallel architecture of the interconnects is designed to match the wide internal bus architectures of devices like CPUs, GPUs, and large ASICs, eliminating the need for power-hungry serialization-deserialization (SerDes) interfaces. It enables the separation of devices like GPUs and high bandwidth memory (HBM), improving the thermal performance of HPC systems (Figure 2).

Summary

UCIe was developed to serve the needs of chiplet integration. It includes an interface suited for copper and optical interconnects inside the chiplet. When combined with the CXL protocol, it can extend optical connectivity to external systems like racks in data centers. The initial OIO platforms based on UCIe are beginning to appear for advanced designs.

References

AI and LLMs Limited by Memory Bandwidth, Avicena

Enabling Optical Interconnects Using the New UCIe Standard, Ayer Labs

How Optical Interconnects Enable Data Center Disaggregation, Synopsys

Leveraging Optical Chip-to-chip Connectivity to Unleash the Complete Potential of AI, Edge AI + Vision Alliance

Multi-Die SoCs Gaining Strength with Introduction of UCIe, Synopsys

Two Startups are bringing Fiber to the Processor, IEEE Spectrum