Andes Technology announced its newly-released AndeStar V5 CPU cores – N25/N25F, NX25/NX25F, A25 and AX25 – support the Andes Custom Extension (ACE) feature. The AndeStar V5 architecture is the result of RISC-V technology incorporated with Andes innovations based on rich experience in serving embedded processor IPs for over 10 years. The ACE feature enables embedded designers to add customized instructions on their Andes V5 CPU cores with ease.

RISC-V is an open processor instruction set architecture (ISA) standardized by the non-profit RISC-V Foundation. It is rapidly gaining popularity in many markets because of its compactness, modularity and extensibility. In addition to general-purpose usages, RISC-V specification encourages customized instruction extensions to facilitate the design of Domain-Specific Architecture/Acceleration (DSA) for applications such as Artificial Intelligence/Machine Learning, AR/VR, ADAS, and next-generation storage and networking. Acceleration through customized instructions can boost application performance significantly while maintaining the programmability. Despite the huge benefits that may bring, however, most SoC teams find it difficult to add customized instructions. This is because designing new instructions requires major efforts and CPU talents to modify the existing processor hardware and associated software tools and make sure they work together.

RISC-V is an open processor instruction set architecture (ISA) standardized by the non-profit RISC-V Foundation. It is rapidly gaining popularity in many markets because of its compactness, modularity and extensibility. In addition to general-purpose usages, RISC-V specification encourages customized instruction extensions to facilitate the design of Domain-Specific Architecture/Acceleration (DSA) for applications such as Artificial Intelligence/Machine Learning, AR/VR, ADAS, and next-generation storage and networking. Acceleration through customized instructions can boost application performance significantly while maintaining the programmability. Despite the huge benefits that may bring, however, most SoC teams find it difficult to add customized instructions. This is because designing new instructions requires major efforts and CPU talents to modify the existing processor hardware and associated software tools and make sure they work together.

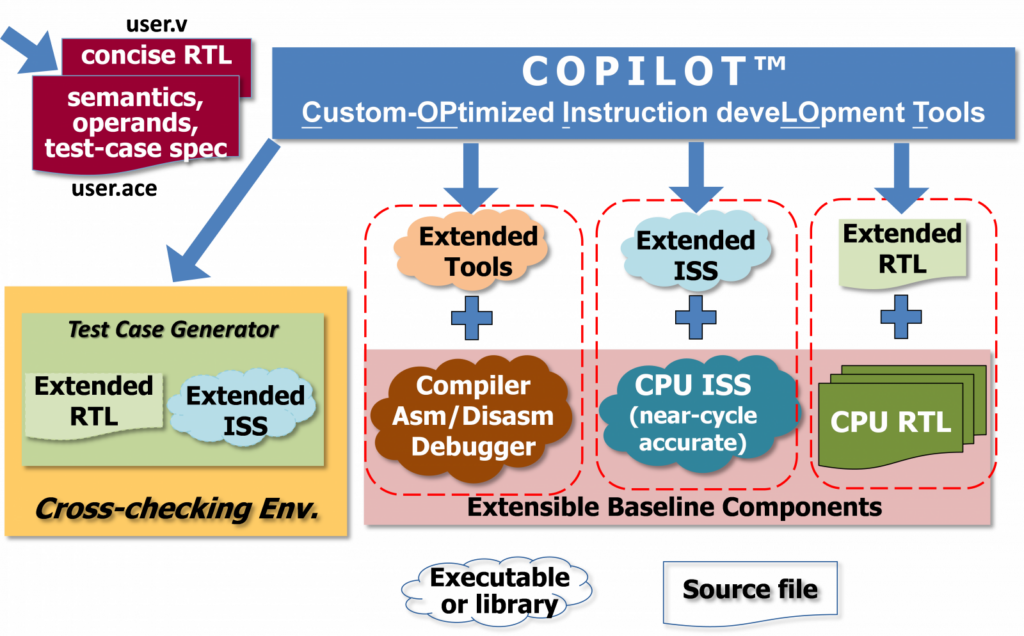

Andes Technology fills this gap by providing the ACE design environment which greatly simplifies the steps to add instructions. By preparing a description file that describes instruction input/output interfaces and instruction semantics in C and a concise Verilog file implementing the RTL logic based on the given interfaces, designers can execute the Custom-OPtimized Instruction deveLOpment Tools (COPILOT) to generate the extended CPU and software toolchains in minutes.

The COPILOT tool is the key to the automatic creation of ACE instruction environment. It offloads all housekeeping RTL design tasks such as opcode selection, instruction decoding, operand mapping, input operand accesses, dependence checking and result gathering. Using ACE needs no expertise in processor pipeline design, thus minimizing the learning curve. Designers can then focus on the implementation of powerful functionalities rather than spend time figuring out how to interact with CPU pipeline.

Andes Custom Extension for AndesCore N25/N25F, NX25/NX25F, A25 and AX25 is available for license now. To explore ACE’s full capabilities, please contact Andes Technology for more information.

Leave a Reply

You must be logged in to post a comment.