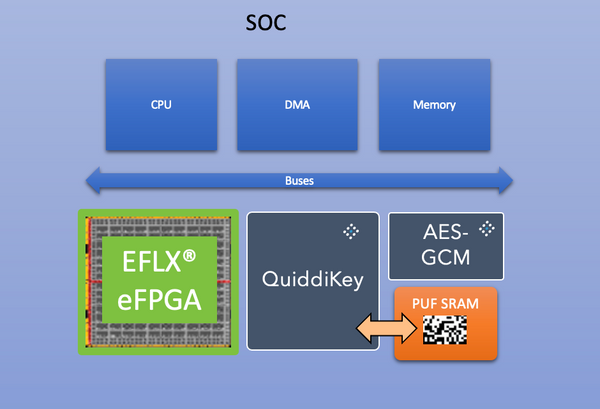

Flex Logix Technologies, Inc. announced that it has partnered with Intrinsic ID to ensure that any device using its eFPGA remains secure and can’t be modified maliciously, whether through physical attacks or remote hacking. The integration of Intrinsic ID SRAM Physical Unclonable Function (PUF) military-grade security IP with Flex Logix’s EFLX eFPGA provides a device unique silicon fingerprint that is used to secure confidential data contained in the bitstream of the eFPGA. If the device is attacked or found in the field, the eFPGA bitstream cannot be read, altered, or copied because the root secret is never stored and therefore invisible and unclonable. This provides a mission-critical level of security to eFPGA customers.

Flex Logix Technologies, Inc. announced that it has partnered with Intrinsic ID to ensure that any device using its eFPGA remains secure and can’t be modified maliciously, whether through physical attacks or remote hacking. The integration of Intrinsic ID SRAM Physical Unclonable Function (PUF) military-grade security IP with Flex Logix’s EFLX eFPGA provides a device unique silicon fingerprint that is used to secure confidential data contained in the bitstream of the eFPGA. If the device is attacked or found in the field, the eFPGA bitstream cannot be read, altered, or copied because the root secret is never stored and therefore invisible and unclonable. This provides a mission-critical level of security to eFPGA customers.

Flex Logix and Intrinsic ID have published a white paper that describes how their partnership is taking eFPGA security to the next level.

The Intrinsic ID SRAM PUF creates a device-unique fingerprint from which a cryptographic root key is extracted. A key derived from this device-unique root key is used to encrypt and authenticate the bitstream of the eFPGA. Suppose the device is attacked or found in the field. In that case, the bitstream of the eFPGA cannot be altered, read, or copied to another device, because it is protected by a key that is never stored and therefore is invisible and unclonable for the attacker.

The main benefits of using the Intrinsic ID SRAM PUF technology over storing a key in non-volatile memory are:

High Security: No key material programmed into the device and no key present when it is not in use.

High Flexibility: Key generation at any time and place in the supply chain without external provisioning.

Low Cost: No dedicated security hardware is required to protect the key, as it is never stored.

Highly Scalable: It employs only standard logic, scaling effortlessly with shrinking technology nodes.

Many markets – 5G, networking, cloud storage, defense, smart home, automotive, and others – are looking to eFPGA to save power and reduce cost. The customer can save power and reduce latency by removing the high-speed SERDES and other unnecessary I/Os or unused peripherals. With embedded FPGA, the end product can take advantage of these benefits and still be reconfigurable in the field, saving time and money.