Faraday Technology Corporation (TWSE: 3035), a leading ASIC design service and IP provider, today introduced the Uranus™ 55nm ultra-low-power SoC development platform for IoT applications. As the latest member of its MCU-based SoC development platform series, UranusTM features Faraday’s PowerSlash™ IP, USB 2.0 interface, 12-bit 8-channel ADC, 10-bit DAC, embedded flash memory, and comprehensive SDK support, demonstrating the next level of IoT chip power-saving.

Faraday Technology Corporation (TWSE: 3035), a leading ASIC design service and IP provider, today introduced the Uranus™ 55nm ultra-low-power SoC development platform for IoT applications. As the latest member of its MCU-based SoC development platform series, UranusTM features Faraday’s PowerSlash™ IP, USB 2.0 interface, 12-bit 8-channel ADC, 10-bit DAC, embedded flash memory, and comprehensive SDK support, demonstrating the next level of IoT chip power-saving.

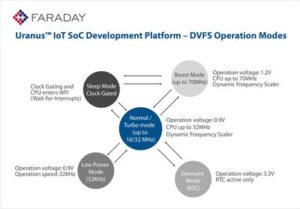

Faraday’s SoC development platform effectively reduces the time-to-market of system products by allowing early software design ahead of chip availability. It offers an integrated environment consisting of mainstream processor core, pre-verified Faraday interface and fabric IP, along with SDK, upon which system software may be built. Further on the premises, Uranus™ platform demonstrates DVFS power modes management to balance trade-offs between performance and power consumption. In particular, its Turbo Mode alters the trade-off point to enable MCU core achieve 2x performance under given power constraint.

“As the driver of ASIC design service innovations, Faraday’s SoC development platform series aims not only to help customer’s chip design but also its system development,” saidSteve Wang, President of Faraday. “Satisfying both ultra-low-power and high-performance needs has become the key for next-generation IoT chip design. We proudly present Uranus™, the newest member of our platform series, to provide the right tool for achieving that goal.”

The post Ultra-low-power SoC development platform targets IoT applications appeared first on Microcontroller Tips.