Confusion often arises around the topic of criteria for picking analog-to-digital converters (ADC). Much discussion is usually given to the sampling rate (also referred to as the conversion rate) which dictates how frequently the source signal must be sampled per second to faithfully reproduce that signal. Twentieth-century electronic communications engineer Harry Nyquist answered that question with the Nyquist rate. The Nyquist rate dictates that any given signal must be sampled at a minimum of twice its maximum component frequency. If not, any component signals above the sampling rate could possibly suffer from aliasing. In other words, higher frequency components could be misinterpreted as a lower frequency signal. Running a signal through a low pass filter tuned to at least one-half of the ADC sampling rate will help to eliminate aliasing concerns.

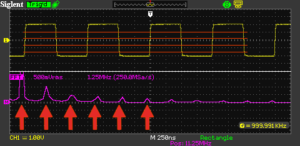

For simple sine waves, this notion is straightforward to visualize. For complex waveforms made up of multiple sine waves, a spectrum analyzer or an oscilloscope with Fast Fourier Transform (FFT) functionality would be needed to discern the various frequency components. We measure the sampling rate in samples per second (sps), or ksps (thousands of samples per second) of Msps (millions of samples per second).

Fig 1a (Top) 5Vpp would have a resolution of ~4.9mV per step. Fig 1b (Bottom) Viewing a 1MHz source signal in the frequency domain can help to visualize the discrete frequency components of complex signals.

Many discussions on ADCs end at this point, but another major factor for analog conversion is the sampling depth. The sampling depth impacts the precision of measuring the voltage level during any given sample or the resolution at which we can look at the amplitude of the source signal. The amount we can quantize an analog signal is given by equation 2n, meaning a signal can be broken into 2n discrete levels. For a 10-bit ADC, there are 210 or 1024 discrete values that we can discern from a given source signal, and we can calculate the resolution from the equation:

Q = [ VPeakHigh – VPeakLow ] / 2n

Using the same 10-bit example from before, if we are sampling a 0V to 5V signal than the smallest change in signal we can detect is [5V – 0V] / 1024, which is approximately 2.5mV. Of course, this is academic and in the real-world, resolution is limited by noise and other sources of distortion, which causes SINAD or Signal-to-Noise and Distortion Ratio. Practically speaking, there is an effective limit on the resolution. If the datasheet of the ADC gives the SNR (Signal-to-Noise Ratio) of the device, then it is possible to calculate the Effective Number of Bits (ENOB) using the formula:

ENOB = [SNR(dB) – 1.76dB ] / 6.02dB

One final aspect of ADCs that should be considered is called step recovery. Put simply; step recovery dictates how fast the output of an ADC can respond to a change in the input. This has more to do with the topology of the ADC design and can vary greatly from one type of ADC to the next.

Practically speaking, the variety of families of ADCs each have their strengths and weaknesses that must be considered from an application specific perspective. Designers must also consider interface technologies (e.g., I2C, SPI, etc.) and power versus speed. Some general rules of thumb are:

Successive Approximation Register: For medium to high-speed applications (100s ksps to a few MSPs) and shallow sampling depths (less than 16-bits);

Delta-Sigma: For medium speed high applications (measured in 100s ksps to low Msps) and deeper sampling depths (16-bits or greater);

Slope Integrating (single, dual, quad-slope): Good for low-speed applications (10s to 100s samples per second); and

Flash or Direct Conversion: For very high-speed applications that are measured in 100s of Msps.

Leave a Reply

You must be logged in to post a comment.